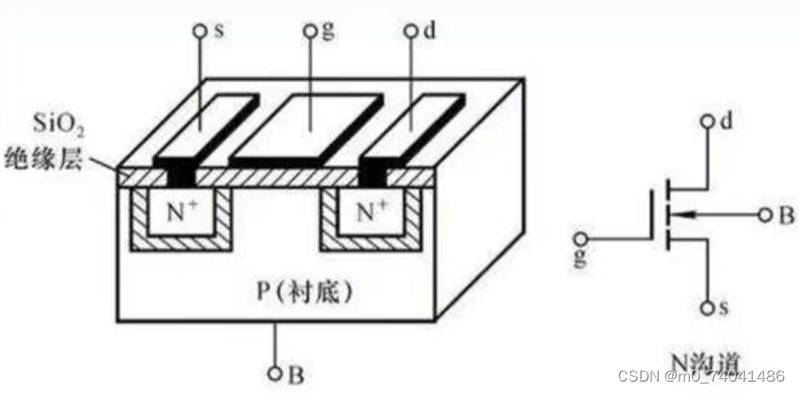

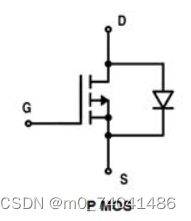

NMOS结构示意图

如下图所示:

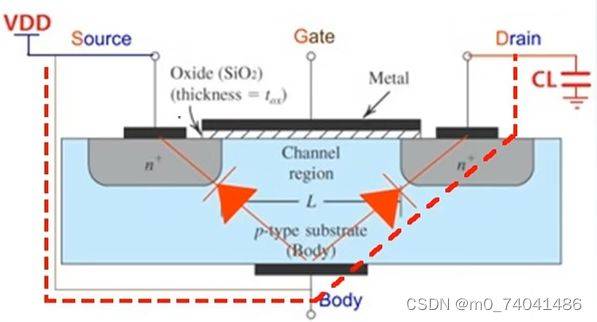

如上图所示,NMOS是用一块掺杂浓度较低的P型硅片作为衬底,利用扩散工艺在衬底上扩散出两个高掺杂浓度的N型区(N+),并在此N型区上引出两个欧姆接触电极,分别称为源极(s)和漏极(d)。在源极漏极之间的衬底表面覆盖一层二氧化硅(SiO2)绝缘层,叫栅氧化层或栅绝缘层,在此绝缘层上沉积出金属铝层并引出电极作为栅极(g)。从衬底引出一个欧姆电极称为衬底电极(B)。

在MOS管中,源极为提供载流子的端子,而漏极为接收载流子的端子。NMOS管的源极通常连接至电路的最低电位,而源极连接至电路的最高电位。

源极S和漏极D与衬底之间形成了两个PN结即两个二极管。

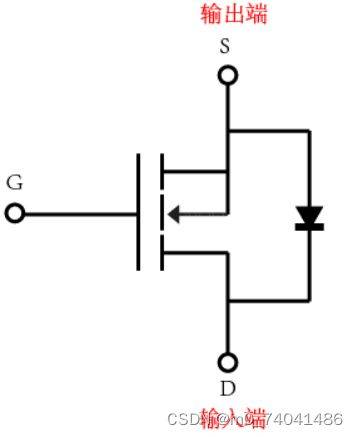

市面上出售的绝大多数NMOS,衬底B通常与源极S连接在一起,这样两个电极的电位是一致的,可以避免体效应引起的阈值电压的飘移。因为衬底B与源极S连接在一起,所以衬底B和源极S之间的二极管被短路,只剩下衬底B与漏极D之间的二极管,积源极S与漏极D之间的体二极管图如下所示。

观察该图,源极S处箭头方向为电子移动方向

体二极管(漏源二极管)有关的参数:

:二极管正向电流

:二极管正向电压

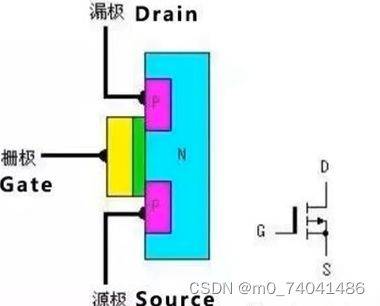

PMOS结构示意图

PMOS结构与上面的NMOS类似,源极S和漏极D与衬底B形成两个二极管,连接源极S和衬底B,源极S和衬底B之间的二极管被短路,只剩漏极D和衬底B之间的二极管即漏极D与源极S之间存在一个体二极管

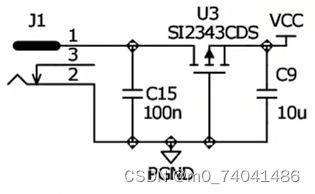

PMOS的应用: 可以做电子开关:

当1接高电平,2接低电平时,栅极G为低电平,源极S为VCC高电平,PMOS导通;当1接低电平,2接高电平时,栅极G和源极S都为高电平,PMOS不导通,且体二极管方向为漏极D指向源极S,为截止状态。

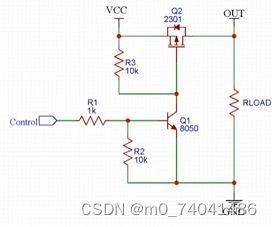

Control端接低电平,三极管不导通,源极S和栅极G相连都为高电平,PMOS不导通;Control端接高电平,三极管导通,栅极G接地,源极S接高电平,PMOS导通。

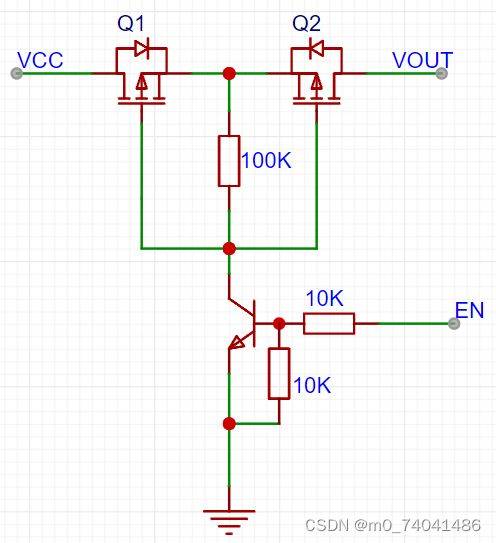

防漏电:

由于Q1体二极管的存在,所以Q1的源极和Q2的源极与VCC相连都为高电平

EN端输入低电平,三极管截止,Q1和Q2的源极和栅极都为高电平,所以Q1和Q2都不导通,VOUT不输出。EN端输入高电平,三极管导通,Q1和Q2栅极接低电平,源极接高电平,都导通,VOUT输出。Q1和Q2的两个体二极管方向相反,使得能够完全关断电源而不漏电。

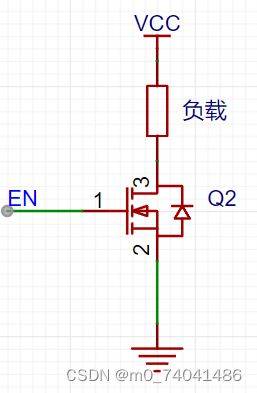

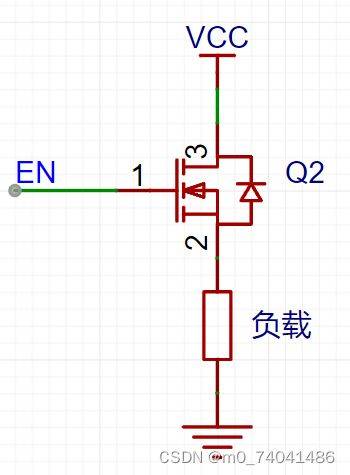

NMOS的应用: 做电子开关:

EN端为低电平,NMOS栅极和源极都为低电平,不导通。EN端为高电平,栅极为高电平,源极为低电平,导通。

NMOS的负载不能接在低端。若负载接在低端,EN为低,源极为低,不导通。EN为高,若导通则负载上端为高,可是这样栅极和源极都为高,那么不导通。(这样接必须加自举电路)

若用单片机控制MOS管,最好在控制脚处加一个100欧姆电阻。

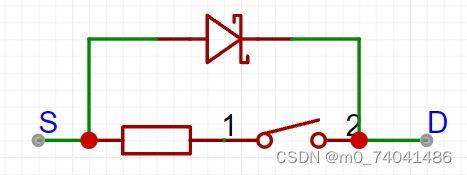

NMOS等效示意图:

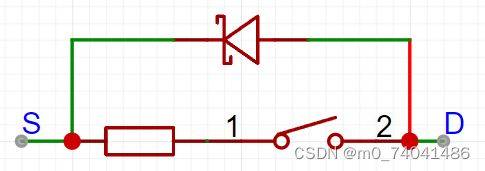

PMOS等效示意图:

MOS管参数:

:漏极D和源极S之间的电压。

:漏极D和源极S之间的等效电阻。越小越好,越小消耗的功率越小,发热越少。

:栅极G和源极S之间的电压阈值(门限电压)。

:持续漏极电流。

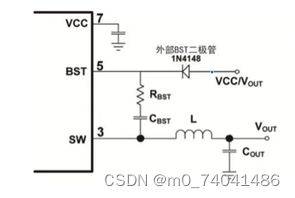

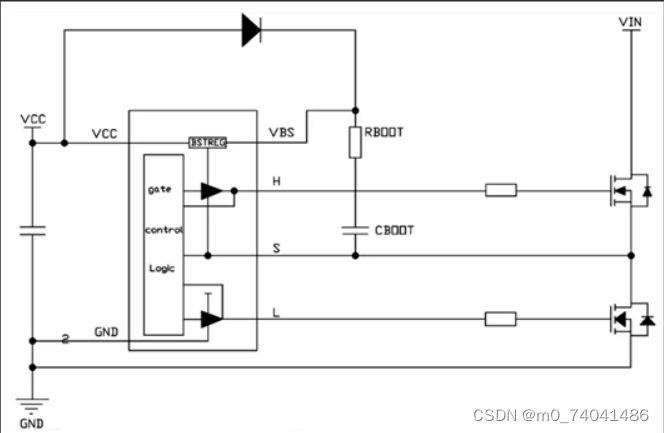

自举电路:

在NMOS管的源极S和漏极D之间接一个自举电容(BST电容)。

H为低电平时,L为高电平,上管关闭,下管导通,BST电容CBOOT通过VCC充电,充电时间为下管导通时间记作

;H为高电平时,L为低电平,下管关闭,由于电容两端电压不能突变,所以CBOOT上端电压被举起。如此上管栅极S电压就大于源极S电压,上管导通,此时VBOOT电压通过RBOOT和内部电路放电,放电时间为记作

BST电容的选型

要用好一点的电容,最好用COG,最次也要用X7R,大小不能太大也不能太小(0.1uF-1uF),控制好充放电时间。一般建议BST电容与一个小电阻(20欧姆)串联,来降低尖峰电压。但是阻抗变大会损失部分效率。

外部BST二极管提升效率

当占空比很高(大于等于0.65)时,可以使用一个外部BST二极管(1N4148)提升效率。可以使用2.5V和5V之间的一个电源给外部BST二极管供电,如下图所示。